# Criticality Driven Execution

Aniket Deshmukh

# High Performance Systems Group Department of Electrical and Computer Engineering The University of Texas at Austin Austin, Texas 78712-0240

TR-HPS-2025-001 June, 2025 Copyright

by

Aniket Deshmukh

2025

# The Dissertation Committee for Aniket Deshmukh certifies that this is the approved version of the following dissertation:

# Criticality Driven Execution

#### Committee:

Yale N. Patt, Supervisor

Mattan Erez

Poulami Das

Christopher J. Rossbach

Rustam R. Miftakhutdinov

## Criticality Driven Execution

# by Aniket Deshmukh

#### Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2025

## Acknowledgments

Many people contributed both directly and indirectly, in big and small ways, to help me reach where I am today.

Beginning, of course, with my family. My parents continue to be my biggest supporters in whatever path I choose. My mum, Anjali Deshmukh, is the closest confidant and friend I have ever had. She raised me to be loving and kind, open-minded and independent, to learn to live with myself through all my shortcomings and weaknesses. Our conversations - over everything from philosophy, science, technology, Yoga, and the like helped me grow and understand both myself and the world around me in a way I could never have managed on my own. I only hope that I can continue to support her in the best way I can and carry forward her spirit of giving back to society.

My baba, Aashish Deshmukh, has always been my strongest pillar of support. His dedication toward excellence and discipline was what drove me to perform to the best of my ability, no matter what the task. However, his love and care shone through in many moments - when he gave me my first Isaac Asimov book, when he helped me with fluid mechanics during my entrance exams, but most prominently: when I chose to do my PhD. I still remember him saying, "Take as long as you want, study all your life if you wish. We are here to support you emotionally and financially, so don't hold yourself back." These words gave me the confidence to push forward without fear, and I cannot thank him enough for that.

Toward my younger brother, Aneesh Deshmukh, I feel a great debt. We've had fun times together, but I feel I wasn't there for him when he was going through tough times during my undergraduate years, yet he was there to lend me an ear and listen to all my troubles over the course of my PhD. I can only hope you lean on me more for support. My cousin, Shivansh Dutt, ever a bundle of energy, made sure the time we spent over the years was always insane fun. I thank my aunt, Anuradha

Harke, and my grandmother, Shakuntala Harke, for always greeting me with a smile when I go back home to India and for all the amazing food I can never get anywhere else in the world.

I thank all my friends in Austin for their company over these past few years. Prateek, Wenqi, and Anyesha, who joined the PhD program alongside me, have been constant companions, both in the office at EER and outside. I thank Abbie, who was happy to chat over coffee anytime, and Jaegun, for being a good friend and driving me from time to time. I thank Divija, Jaeyong, Andrew, Margaret, and Rathna, among the juniors, for going along with anything I planned. Special thanks to Kayvan and Matthew for proofreading everything I gave them, and of course, for their great company, especially over the past summer.

I thank Ali and Kayvan, who helped me sound out my research ideas and listened to all my rants, Sophia, who was always willing to help out with everything and always had food for us, and Evan, who wasn't around for long but fit perfectly into our CBP team.

I haven't been in touch with folks back in India as much as I should have - Aditya, Masroor, and the rest of the Class-VIII group. But the few chances we did have to talk always reminded me of the good times.

During my internships, I met many people who helped me grow professionally and provided perspective on how the industry works. I thank Doug Carmean for giving me the freedom to explore as much as I wanted at Microsoft, and especially Rob Chappell, who helped me mold the core ideas for my dissertation early on. I thank Jayesh Gaur and John Combs for my time at Intel. I am grateful to Niket, Mo, Rustam, and Kulin for fully supporting me during my two final Apple internships and giving me the opportunity to work on engaging projects.

I enjoyed the advice and company of all the UT professors. I thank Mattan Erez for his honest opinion on everything, and Poulami Das for all her advice.

One of the biggest aspects of my time as a PhD student was being part of the HPS research group. Faruk often drove me home after our group meetings, and chatting with him about his hobbies and life in general was a lot of fun. Despite being the most senior student when I first joined, he made me feel truly welcome. There was never a dull moment with Ben around - his comments always kept things interesting, and his assistance with all my memory-related questions was invaluable.

In Stephen, I saw someone going through similar struggles to mine and coming out on top. His advice on how to conduct research and how to speak clearly to convey your ideas helped me through my middle PhD years, when I really struggled, and I am thankful to him for this. Siavash was always welcoming and happy to talk about whatever I wanted - research, personal life, or just to go get fried chicken, which I really appreciate.

The last seven years of my PhD wouldn't have been enjoyable without Chester. Ever since my first publication, the two of us have talked about research so often that we've probably memorized the intricacies of each other's work by now. Having someone with whom you can discuss everything: basketball, food, life in general, and almost everything else under the sky made me feel I wasn't in this alone, and I truly thank Chester for that. I also thank Leticia, who, as part of the staff, supported the group with all our administrative needs.

I thank all my PhD committee members—Mattan Erez, Chris Rossbach, Poulami Das, and Rustam Miftakhutdinov—for their support and feedback, which went a long way towards ensuring the dissertation was up to the mark. I also thank them for adjusting to what was a very hectic timeline in the last few months.

Finally, I thank Dr. Patt for all he has taught me over the last eight years. His ability to explain complex concepts so simply that even students fresh out of high school could understand stuck with me when I first TAed for him, and has always been a goal I wish to achieve someday. As a young PhD student who joined the group, he encouraged me to freely explore the breadth and depth of computer architecture

research, which helped me build a strong foundation. As his head TA, he showed me the importance of being sharp, precise, and meticulous in everything I did. These were also some of the best times I had teaching students, and I thank him for this opportunity. Above all, I thank him for his trust in me, which allowed me to achieve this milestone of completing my PhD dissertation.

-Aniket, April 2025, Austin, TX

#### Abstract

#### Criticality Driven Execution

Aniket Deshmukh, PhD The University of Texas at Austin, 2025

SUPERVISOR: Yale N. Patt

Modern out-of-order (OoO) cores achieve high single-thread performance by maintaining a steady instruction supply through accurate branch prediction and reducing memory access latencies using data prefetchers and a cache hierarchy. Despite advancements in prediction algorithms and data prefetching techniques, the remaining branch mispredictions and cache misses still present major bottlenecks in many applications. Moreover, these bottlenecks often overlap in many applications - accelerating them together is vital for extracting the full benefit associated with solving these bottlenecks. Most prediction alternatives proposed in academia, like precomputation and runahead execution, only target either branch misprediction or cache misses and provide limited coverage. While solutions that target both branches and load like Slipstream exist, they require significant area, power, and energy investment.

This work provides a holistic approach for reducing the performance penalty associated with a significant fraction of these branch mispredictions and cache misses, without needing any additional execution hardware. Criticality Driven Execution (CDE) constructs accurate and lightweight dependence chains that issue early pipeline flushes for hard-to-predict branches and improve Memory Level Parallelism for long-latency loads simultaneously. It combines speculative precomputation—executing

specific chains twice—with instruction reordering that prioritizes the fetch and allocation of the remaining chains, accelerating the execution of these "critical" chains while maintaining high coverage. CDE dynamically redistributes existing OoO core resources to prioritize critical chains at the cost of delaying and providing fewer resources to "non-critical" instructions, achieving a 9% performance improvement without requiring a dedicated execution engine or separate OoO core.

# Table of Contents

| List of | Tables                                                     | 15 |

|---------|------------------------------------------------------------|----|

| List of | Figures                                                    | 16 |

| Chapte  | r 1: Introduction                                          | 18 |

| 1.1     | The Problem                                                | 18 |

|         | 1.1.1 Impact of Branch Mispredictions and Cache Misses     | 19 |

|         | 1.1.2 Limitations of the Existing Execution Model          | 20 |

| 1.2     | Criticality Driven Execution                               | 21 |

|         | 1.2.1 Identifying Critical Instructions                    | 22 |

|         | 1.2.2 Precomputation for Hard-To-Predict Branch Chains     | 22 |

|         | 1.2.3 Preferential Allocation for Long-Latency Load Chains | 23 |

| 1.3     | Building a Unified Execution Model                         | 24 |

| 1.4     | Contributions                                              | 25 |

| 1.5     | Thesis Statement                                           | 26 |

| 1.6     | Dissertation Organization                                  | 26 |

| Chapte  | er 2: Background and Prior Work                            | 27 |

| 2.1     | Prediction Mechanisms                                      | 27 |

|         | 2.1.1 Branch Prediction                                    | 27 |

|         | 2.1.2 Data Prefetching                                     | 27 |

| 2.2     | Precomputation                                             | 28 |

|         | 2.2.1 Compiler Generated Threads                           | 28 |

|         | 2.2.2 Runtime Precomputation Threads                       | 28 |

|         | 2.2.3 Slipstream                                           | 29 |

|         | 2.2.4 Using Precomputation to Resolve Branches Early       | 30 |

| 2.3     | Runahead Execution                                         | 31 |

| 2.4     | Compiler Solutions                                         | 32 |

| 2.5     | Other Related Work                                         | 32 |

| 2.6     | Baseline Out-Of-Order Core                                 | 33 |

| Chapte  | er 3: Critical Chain Construction                          | 35 |

| 3.1     | Marking Hard-To-Predict Branches and Long-Latency Loads    | 35 |

|         | 3.1.1 Critical Count Tables                                | 35 |

| 3.2     | Identifying Dependence Chain Instructions                  | 36 |

|         | 3.2.1 Fill Buffer                                          | 37 |

|        | 3.2.2  | Backward Dataflow Walk                                          | 37 |

|--------|--------|-----------------------------------------------------------------|----|

|        | 3.2.3  | Storing Dependence Chain Instructions                           | 10 |

| 3.3    | Track  | ing Memory Dependencies                                         | 10 |

| 3.4    | Tracin | ng Longer Dependence Chains                                     | 10 |

| 3.5    | Comb   | ining Chains across Multiple Control Flows                      | 11 |

| 3.6    | Stead  | y State Operation                                               | 13 |

|        | 3.6.1  | Block Cache                                                     | 13 |

| 3.7    | Recon  | structing the Dependence Chains at Fetch                        | 15 |

| Chapte | r 4: S | peculative Precomputation for Hard-To-Predict Branch Chains . 4 | 18 |

| 4.1    | CDE I  | Precomputation Thread                                           | 18 |

|        | 4.1.1  | Benefits of using the Main Branch Predictor                     | 19 |

|        | 4.1.2  | Load Prefetching Effect                                         | 51 |

| 4.2    | Imple  | mentation Overview                                              | 51 |

| 4.3    | Fronte | end                                                             | 52 |

|        | 4.3.1  | Fetch                                                           | 53 |

|        | 4.3.2  | Rename and Allocation                                           | 53 |

| 4.4    | Backe  | nd                                                              | 53 |

|        | 4.4.1  | Freeing Physical Registers                                      | 54 |

|        | 4.4.2  | Dealing with Stores                                             | 55 |

|        | 4.4.3  | Branch Misprediction Flushes                                    | 56 |

|        | 4.4.4  | Terminating the CDE Precomputation Thread                       | 57 |

| 4.5    | Hardv  | vare Overhead                                                   | 59 |

| 4.6    | Evalua | ation                                                           | 60 |

|        | 4.6.1  | Methodology                                                     | 60 |

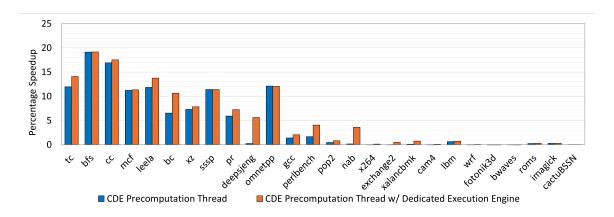

|        | 4.6.2  | Performance                                                     | 60 |

|        | 4.6.3  | Load Prefetching Effect                                         | 3  |

|        | 4.6.4  | Varying the Precomputation Thread Density                       | 66 |

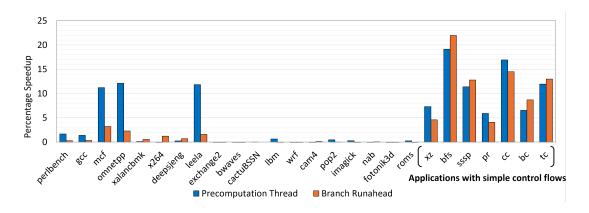

|        | 4.6.5  | Comparison against Branch Runahead                              | 37 |

|        | 4.6.6  | On-Core vs Dedicated Execution Engine                           | 38 |

|        | 4.6.7  | More Sensitivity Studies                                        | 38 |

| Chapte | r 5: F | Preferential Allocation for Long-Latency Load Chains            | 70 |

|--------|--------|-----------------------------------------------------------------|----|

| 5.1    | Impro  | oving Memory Level Parallelism                                  | 70 |

|        | 5.1.1  | Partitioning Backend Resources                                  | 71 |

|        | 5.1.2  | Impact on Branch Misprediction Latency                          | 72 |

| 5.2    | Front  | end                                                             | 73 |

|        | 5.2.1  | Fetch                                                           | 73 |

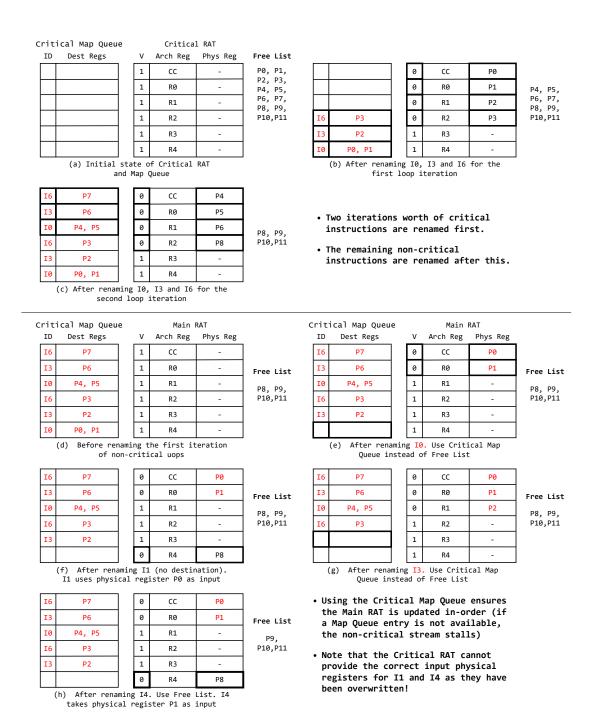

|        | 5.2.2  | Rename                                                          | 73 |

|        | 5.2.3  | Dependence Violations in the Critical Stream                    | 76 |

| 5.3    | Backe  | end                                                             | 77 |

|        | 5.3.1  | Scheduling                                                      | 77 |

|        | 5.3.2  | Dynamically Changing the Partition Sizes                        | 77 |

|        | 5.3.3  | Branch Mispredictions                                           | 78 |

|        | 5.3.4  | Consistency Considerations and Memory Disambiguation            | 78 |

|        | 5.3.5  | In-Order Retirement                                             | 78 |

|        | 5.3.6  | Terminating Preferential Allocation                             | 79 |

| 5.4    | Hardy  | ware Overhead                                                   | 79 |

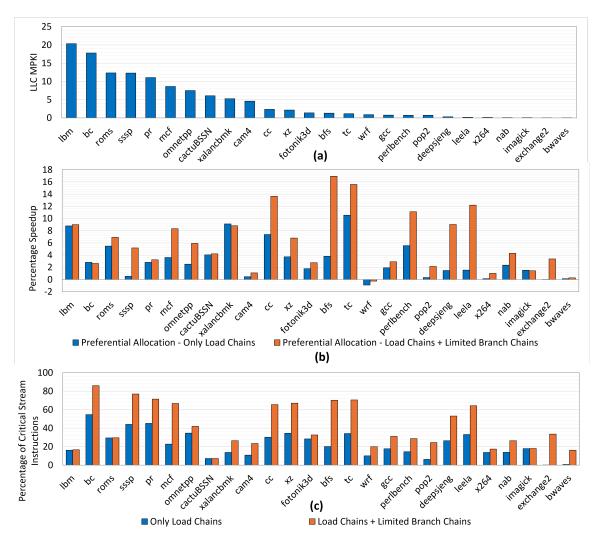

| 5.5    | Evalu  | ation                                                           | 80 |

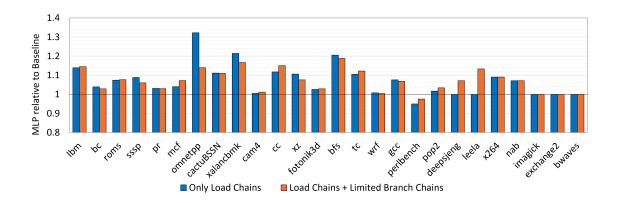

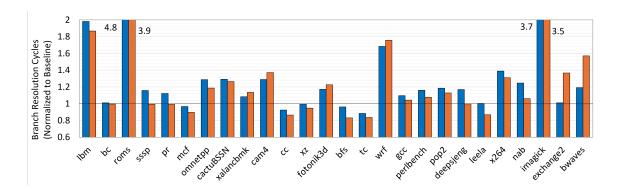

|        | 5.5.1  | Performance                                                     | 80 |

|        | 5.5.2  | Dealing with Branch Mispredictions                              | 82 |

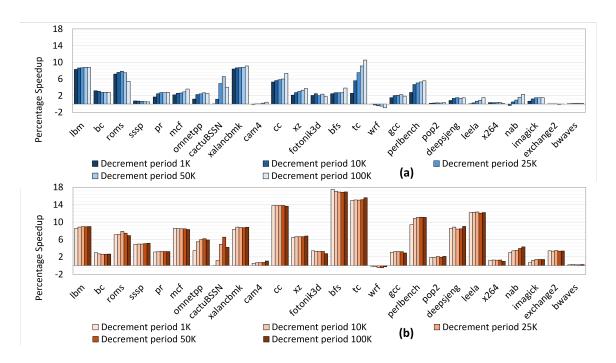

|        | 5.5.3  | Varying the Critical Stream Density                             | 83 |

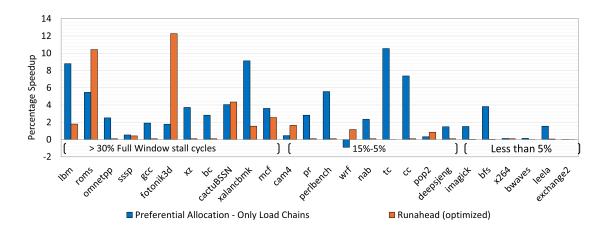

|        | 5.5.4  | Comparison Against Runahead Execution                           | 84 |

|        | 5.5.5  | Reducing the MSHR sizes                                         | 86 |

| Chapte | r 6: E | Building a Unified Model                                        | 87 |

| 6.1    | Perce  | ntage of Instructions in Dependence Chains                      | 87 |

|        | 6.1.1  | Experiment Design                                               | 88 |

|        | 6.1.2  | Benchmark Categorization                                        | 88 |

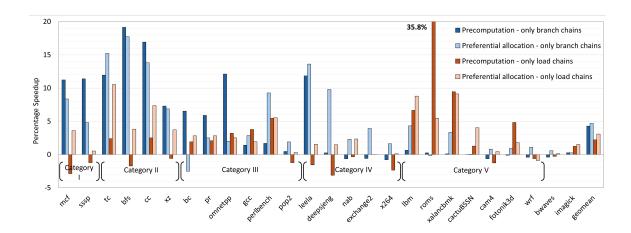

|        | 6.1.3  | Improving Loads and Branches Individually                       | 91 |

| 6.2    | Unifie | ed Execution Model                                              | 92 |

|        | 6.2.1  | Why the Simple Approach does not Work                           | 92 |

|        | 6.2.2  | Accelerating Loads and Branches together                        | 93 |

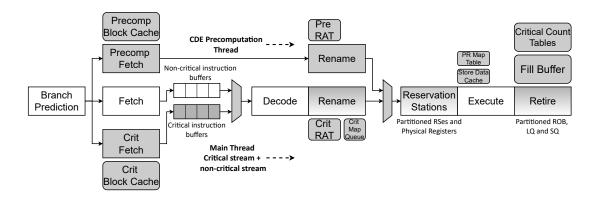

| 6.3    | Imple  | mentation Overview                                              | 94 |

| 6.4    | Tracia | ng Chains for the Precomputation Thread and the Critical Stream | 95 |

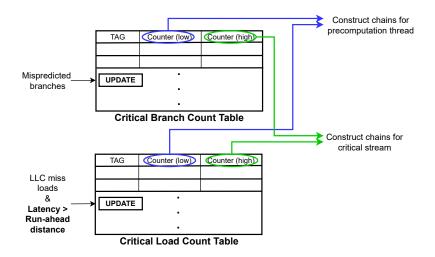

|        | 6.4.1  | Critical Count Tables                                           | 95 |

|        | 6.4.2  | Fill Buffer                                                     | 96 |

|        | 6.4.3  | Backward Dataflow Walk                                          | 96 |

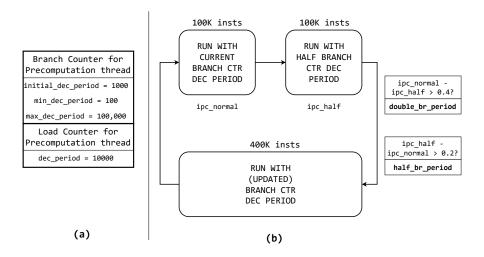

| 6.5     | Dynamically Adjusting how Chains are Accelerated    | 97  |

|---------|-----------------------------------------------------|-----|

| 6.6     | Frontend Changes for the Unified Model              | 98  |

|         | 6.6.1 Fetch                                         | 98  |

|         | 6.6.2 Rename                                        | 99  |

|         | 6.6.3 Allocation                                    | 99  |

| 6.7     | Backend Changes for the Unified Model               | 99  |

| 6.8     | Hardware Overhead                                   | 99  |

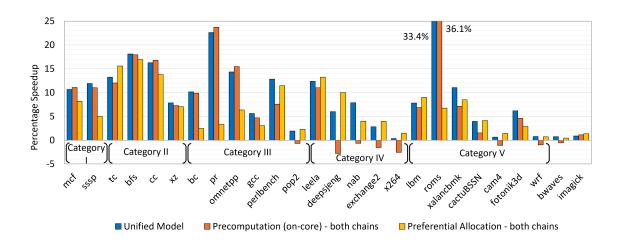

| 6.9     | Evaluation                                          | 100 |

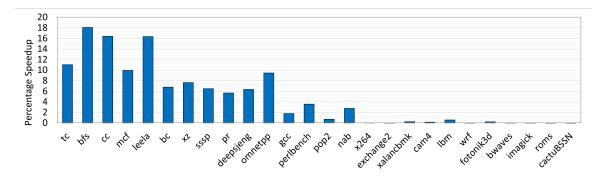

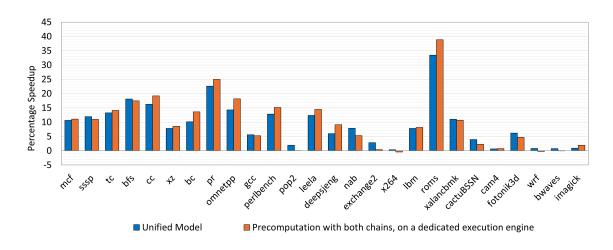

|         | 6.9.1 Performance                                   | 100 |

|         | 6.9.2 Misprediction Coverage                        | 102 |

|         | 6.9.3 Comparison against a Slipstream-Like Approach | 103 |

|         | 6.9.4 Parameter Tuning                              | 104 |

| Chapte  | r 7: Conclusion and Future Work                     | 105 |

| 7.1     | Conclusion                                          | 105 |

| 7.2     | Future Work                                         | 106 |

| Referen | CAS                                                 | 108 |

# List of Tables

| 2.1 | Core parameters                                                                                                          | 33 |

|-----|--------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Fill Buffer entry                                                                                                        | 37 |

|     | Structure sizes for the CDE precomputation model Percentage of branch mispredictions for which the full penalty is saved |    |

| 5.1 | Structure sizes for the preferential allocation model                                                                    | 73 |

| 6.1 | Benchmark categories based on chain properties                                                                           | 90 |

# List of Figures

| 1.1  | Eliminating all branch mispredictions and D-Cache misses                       | 18 |

|------|--------------------------------------------------------------------------------|----|

| 3.1  | Identifying dependence chain instructions in the Fill Buffer                   | 38 |

| 3.2  | Tracing longer dependence chains using previously marked instructions          | 41 |

| 3.3  | Tracing dependence chains across multiple control flows                        | 42 |

| 3.4  | Implementation overview: Tracing dependence chains                             | 44 |

| 3.5  | Fetching uops from the Block Cache                                             | 46 |

| 4.1  | CDE precomputation thread example                                              | 48 |

| 4.2  | Implementation overview: Precomputation for hard-to-predict branches           | 51 |

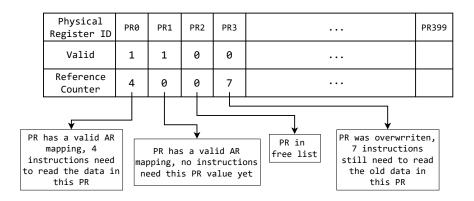

| 4.3  | Physical Register Map Table                                                    | 55 |

| 4.4  | Example of an incorrect precomputation thread                                  | 58 |

| 4.5  | Sequence of events leading up to the detection of an incorrect chain .         | 58 |

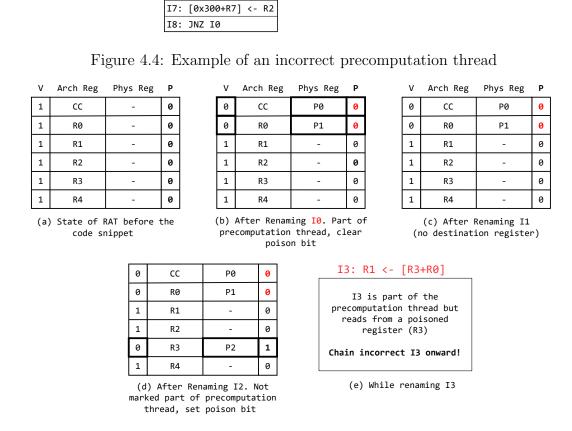

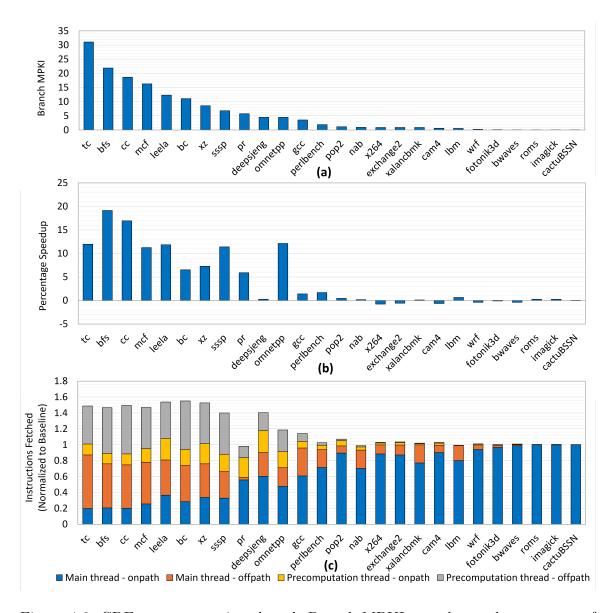

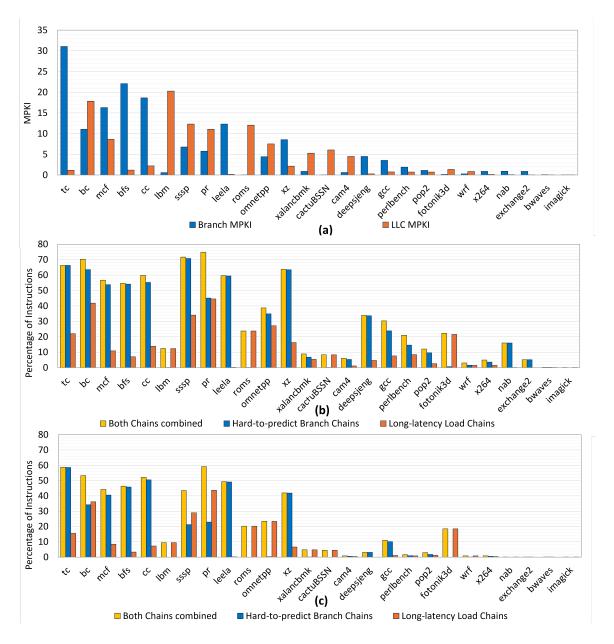

| 4.6  | CDE precomputation thread: Branch MPKI, speedup and percentage of instructions | 61 |

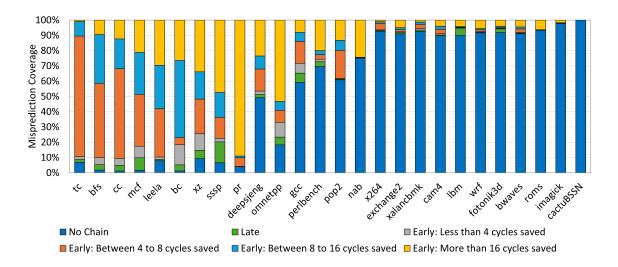

| 4.7  | Branch misprediction coverage                                                  | 62 |

| 4.8  | Run-ahead distance                                                             | 64 |

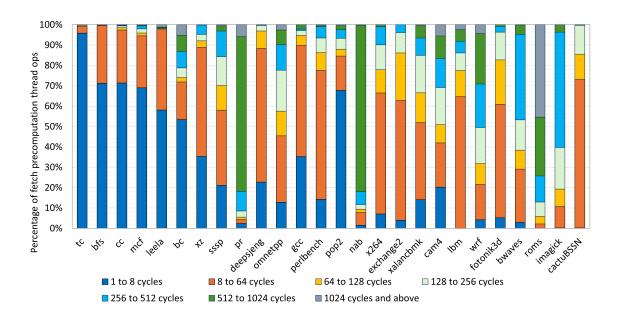

| 4.9  | Distribution of main thread load accesses that miss in the D-Cache  .          | 65 |

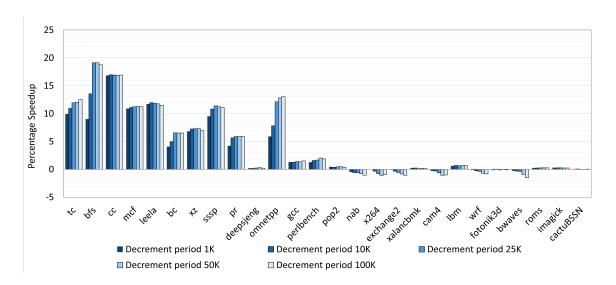

| 4.10 | Performance for different Critical-Branch Count Table decrement periods        | 66 |

| 4.11 | Comparison against Branch Runahead                                             | 67 |

| 4.12 | Speedup with a dedicated execution engine                                      | 68 |

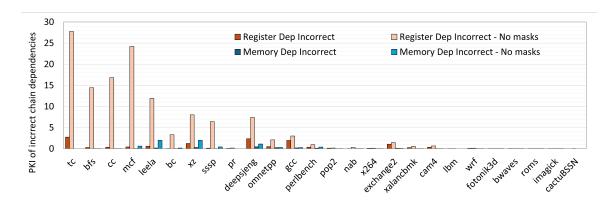

| 4.13 | Incorrect chains detected per 1000 instructions                                | 69 |

| 4.14 | Relative Speedup with 32 Functional Units in the Baseline                      | 69 |

| 5.1  | Preferential allocation example                                                | 70 |

| 5.2  | Implementation overview: Preferential allocation for load-latency loads        | 72 |

| 5.3  | Renaming in preferential allocation: An example                                | 74 |

| 5.4  | Renaming in preferential allocation: An example (continued)                    | 75 |

| 5.5  | Preferential allocation: LLC MPKI, speedup, and percentage of instructions     | 81 |

| 5.6  | Memory-Level Parallelism                                                       | 82 |

| 5.7  | Branch resolution latency, normalized to baseline                              | 83 |

| 5.8  | Performance for different Critical-Load Count Table decrement periods          | 84 |

| 5.9  | Comparison against Runahead Execution                                                   | 85  |

|------|-----------------------------------------------------------------------------------------|-----|

| 5.10 | Using 24 MSHRs in the Baseline                                                          | 85  |

| 6.1  | Distribution of chain instructions                                                      | 89  |

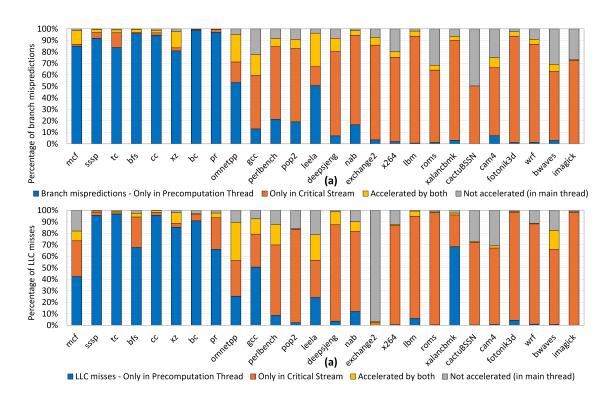

| 6.2  | Accelerating only hard-to-predict branch chains or long-latency load chains             | 91  |

| 6.3  | Implementation overview: Unified execution model for CDE                                | 95  |

| 6.4  | Critical Count Tables with two counters                                                 | 96  |

| 6.5  | Tracing chains in the combined model                                                    | 97  |

| 6.6  | Dynamically adjusting the decrement period for precomputation thread branches and loads | 98  |

| 6.7  | Speedup of the unified execution model                                                  | 100 |

| 6.8  | Branch misprediction and LLC miss coverage                                              | 102 |

| 6.9  | Comparison against a Slipstream-Like approach                                           | 103 |

## **Chapter 1: Introduction**

#### 1.1 The Problem

Single-thread performance remains an important aspect of improving program runtime on out-of-order (OoO) cores. These cores require a steady instruction supply and fast memory accesses for high performance. The instruction supply is provided by a wide fetch unit coupled with an accurate branch predictor, while a multi-level cache hierarchy supported by data prefetchers reduces effective load latencies. However, despite decades of research, interruptions in instruction supply caused by branch mispredictions and backend stalls caused by cache misses that cannot be prefetched remain the two biggest limitations for OoO execution.

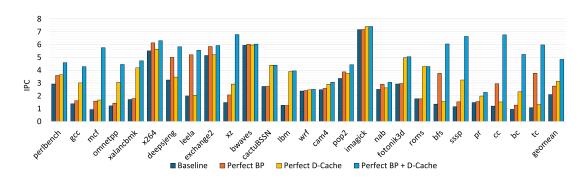

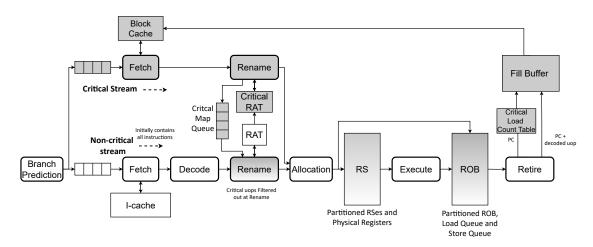

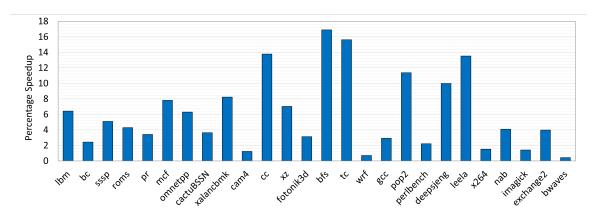

Figure 1.1: Eliminating all branch mispredictions and D-Cache misses

Figure 1.1 illustrates the potential performance gains if these bottlenecks are addressed in an 8-wide OoO core<sup>1</sup>. Eliminating all branch mispredictions (for both direct and indirect branches) improves Instructions Per Cycle (IPC) by 32%, and a perfect D-Cache provides a 49% IPC improvement. However, prior work has shown that these bottlenecks overlap in many applications [9]. Addressing them together reveals their true performance potential, and as seen in the final bar in Figure 1.1,

$<sup>^1{\</sup>rm Using}$  a TAGE-SCL branch predictor and an aggressive Stream Prefetcher. The configuration for the baseline core is provided in Table 2.6

this provides a multiplicative speedup of 2.3x. Interestingly, a small subset of static branches and loads ( $\sim 256$ ) is responsible for over 95% of branch mispredictions and load misses — these "hard-to-predict" branches and "long-latency loads" present key opportunities for improving performance.

Over the years, better branch prediction and load prefetching algorithms have been proposed to tackle this problem. However, the improvement in prediction mechanisms has plateaued recently, particularly for the set of hard-to-predict branches and load-latency loads (see Section 2.1). State-of-the-art academic proposals employing large neural networks that are too complex for hardware implementation only address  $\sim 20\%$  of the branch mispredictions [64] (over TAGE-SCL[51]) and only provide  $\sim 30\%$  D-Cache miss coverage [16] (over an aggressive stream prefetcher), leaving a lot of performance on the table. To bridge this gap, this dissertation focuses on mitigating the performance penalty associated with branch mispredictions and cache misses by directly addressing their impact on OoO cores.

#### 1.1.1 Impact of Branch Mispredictions and Cache Misses

A branch misprediction forces the processor frontend to fetch wrong-path instructions until the branch is executed. Once executed, all instructions younger than the mispredicted branch are flushed, and the control flow is corrected. The longer the branch takes to execute, the more cycles wasted on fetching and processing wrongpath instructions. These wrong path fetch cycles are responsible for the bottlenecks associated with hard-to-predict branches, but can be decreased if these branches are fetched and executed faster.

Loads that miss in the Last-level Cache (LLC) take hundreds of cycles to complete, often causing full window stalls. This prevents subsequent instructions from entering the processor backend and beginning execution. LLC misses contribute to most of the performance penalty associated with cache misses<sup>2</sup> and their correspond-

<sup>&</sup>lt;sup>2</sup>A perfect branch predictor and perfect LLC provide an improvement of 2.0x

ing stalls are primarily responsible for the bottlenecks associated with long-latency loads. These stall cycles can be reduced if more long-latency loads are initiated in parallel, which allows their execution latencies to overlap.

Thus, prioritizing the execution of hard-to-predict branches and long-latency loads over other instructions can help reduce their performance penalty. However, these branches and loads cannot be accelerated by themselves- instructions in their dependence chains are necessary for computing the corresponding branch predicates and load addresses. Mispredicted branches, loads that access memory, and instructions in their dependence chains are "critical instructions" as they primarily govern program performance.

#### 1.1.2 Limitations of the Existing Execution Model

Modern processors fetch and allocate<sup>3</sup> instructions in program order, which does not consider criticality. However, there are more "non-critical" instructions than critical ones - over 85% of the dynamic instructions in the SPEC CPU2017 and GAP workloads on average. This larger proportion of non-critical instructions contributes minimally to program runtime but limits critical instruction throughput in two major ways:

Reduction in frontend bandwidth: Critical instructions are sparsely distributed and interleaved with non-critical ones. Consequently, younger critical instructions must wait for older non-critical instructions as fetch is performed in program order. This limits the effective frontend bandwidth for critical instructions, delaying how quickly they enter the processor backend and begin execution.

Fewer window resources: The instruction window from which an OoO core extracts parallelism is determined by the size of its Re-order Buffer, Physical Register File, Reservation Stations, and Load and Store Queues (window resources).

<sup>&</sup>lt;sup>3</sup>Assigning Reservation Stations and Re-order Buffer entries to instructions after Rename

Critical instructions only occupy 26% of the out-of-order window on average during a full window stall (when more window resources are needed). This limits the amount of parallelism extracted from critical instructions, particularly Memory-Level Parallelism (MLP), which requires a large instruction window.

These limitations can be reduced by building a wider frontend to improve fetch bandwidth and a deeper backend to expose more parallelism. However, scaling the OoO core to enable this is expensive as a wider frontend increases pipeline latency [49] and a deeper backend increases area and power exponentially [43]. Moreover, scaling only increases the proportion of resources distributed to non-critical instructions.

#### 1.2 Criticality Driven Execution

This dissertation introduces Criticality Driven Execution, a paradigm that prioritizes the fetch, allocation, and execution of critical instructions within the OoO core. Criticality Driven Execution (CDE) identifies critical instructions by tracing highly accurate (>99%) dependence chains for hard-to-predict branches and long latency loads at runtime. The chains provide over 80% branch misprediction and LLC miss coverage and are accelerated via two distinct execution models.

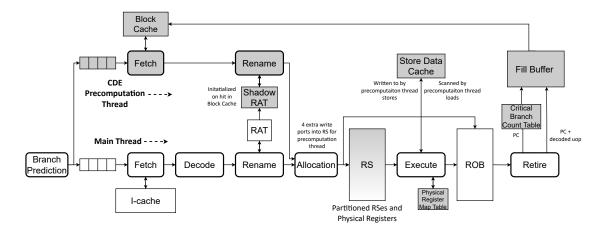

First, CDE combines hard-to-predict branch chains into an independent speculative precomputation thread that issues early pipeline flushes, addressing the frontend bandwidth limitation for these chains. Second, CDE prioritizes the fetch and allocation of long-latency load chains, utilizing backend resources more effectively to improve MLP for these chains. Finally, CDE combines these models to provide a unified solution that addresses both limitations together.

CDE does not use any additional window resources or Functional Units. Noncritical instructions are delayed and allocated fewer resources to prioritize CDE's chains. This allows for more efficient utilization of existing on-core structures without needing to scale the OoO backend or add additional execution hardware.

#### 1.2.1 Identifying Critical Instructions

CDE identifies hard-to-predict branches and long-latency loads at runtime. It then traces their dependence chains, which are long and often span over 10,000 instructions. The chains are broken into basic block-sized segments and stored in a dedicated cache. These segments are stitched together at Fetch (using a decoupled branch predictor) to reconstruct the dependence chains on demand.

This mechanism creates dynamic chains that are accurate for any previously observed control flow, providing far greater branch misprediction and LLC miss coverage compared to prior work (which is limited to tracing chains within simple control flows). The reconstructed chains also contain synchronized timestamps that provide ordering relative to other non-critical instructions.

The chains for hard-to-predict branches and long-latency loads have different properties. Hard-to-predict branch chains generally have lower latencies and should be executed as early as possible to ensure the instruction stream is on the correct path. Long-latency load chains take hundreds of cycles to execute. While these chains benefit marginally from being initiated early, they primarily require a large OoO window so their loads can access memory in parallel. Given the different sources of benefit, CDE uses two different execution models.

#### 1.2.2 Precomputation for Hard-To-Predict Branch Chains

CDE uses an independent, speculative precomputation thread consisting of hard-to-predict branch chains to reduce the misprediction penalty for these branches. This thread is fetched and executed faster as it contains fewer instructions than the full program and triggers early pipeline flushes using the timestamps generated while constructing the branch chains.

The "CDE precomputation thread" uses dedicated Fetch and Rename stages, but shares backend resources with the regular instruction stream (the "main thread"). These resources are freed as soon as possible to allow subsequent precomputation

thread instructions to enter the backend. Precomputation thread instructions are speculative and do not enter the Re-Order Buffer or commit their results. The CDE precomputation thread provides a 4.3% performance improvement over an aggressive baseline OoO core (8.3% for branch-intensive benchmarks). Its higher misprediction coverage allows it to outperform prior work; the CDE chains provide benefit if the precomputation result is ready **before the corresponding main thread branch** is **executed**, compared to prior work that can only use the precomputation result if it arrives **before the corresponding main thread branch** is **fetched**.

Since CDE's chains are highly accurate and timely, they provide high performance when executed on-core, even though this delays the main thread and executes two copies of all precomputation thread instructions (18.7% of the dynamic instructions on average). Using a dedicated execution engine only improves performance by 5.3%, showing that a sizable proportion of the backend resources used by non-critical instructions can be repurposed without hurting performance.

#### 1.2.3 Preferential Allocation for Long-Latency Load Chains

To improve MLP, CDE dynamically reorders the instruction stream by preemptively fetching and allocating resources for long-latency load chains.

This "preferential allocation" model divides window resources - the Re-order Buffer (ROB), Reservation Stations, Load and Store Queues, and Physical Registers - into two partitions. The larger partition is assigned to long-latency load chains, replacing entries usually occupied by non-critical instructions. This allows multiple long-latency loads that normally cannot execute together (due to limited instruction window size) to reside in the backend simultaneously. Preferential allocation thus expands the sequential window from which parallelism can be extracted for critical instructions by skipping over the allocation of non-critical instructions.

Unlike the precomputation approach, the prioritized chain instructions commit their results to avoid the overhead of executing these chains twice. In-order retirement is maintained by comparing the oldest instructions in each partition, facilitated by the timestamps generated during chain construction.

This approach improves performance by 6%<sup>4</sup>, higher than prior work targeting MLP improvement, such as Runahead. Variants of Runahead execution can only discover MLP during full window stalls, which are limited in processors with larger instruction windows. Preferential allocation, on the other hand, proactively discovers MLP by grouping and executing highly accurate long-latency load chains and is energy efficient as no duplicate instructions enter the backend.

#### 1.3 Building a Unified Execution Model

Improving the performance of both hard-to-predict branches and long-latency loads simultaneously requires prioritizing certain chains depending on their properties.

The simple approach - combining both types of chains into one large precomputation thread has several limitations. Combining these chains increases the density of the precomputation thread, causing significant backend contention. Supporting this bigger thread requires a separate core or dedicated execution engine with enough window resources and functional units (as many as the OoO core itself) to avoid backend contention. Prior work targeting branch and load chains simultaneously, like Slipstream [60, 59] and Speculative Multithreading [34], opted for this approach. The additional hardware roughly doubles the backend area and power. Moreover, a larger combined thread limit the effective fetch bandwidth for hard-to-predict branch chains in some applications. This reduces the benefit, even with a dedicated execution engine.

The preferential allocation model prioritizes critical instructions without executing them twice and does not increase backend contention. While preferential

<sup>&</sup>lt;sup>4</sup>Preferential allocation with just load delays branch resolution, and thus needs to prioritize some branch chains as well. Without branch chains, the performance gain is 3.1%

allocation can provide some benefit with hard-to-predict branch chains, it is limited by ROB capacity and in-order retirement, and thus runs much slower than the precomputation thread.

Combining the two models provides a means to optimize for both timeliness (faster chains) and coverage. The precomputation thread mainly targets hard-to-predict branch chains and a few long-latency load chains that benefit from early initiation, keeping it lightweight and timely. Preferential allocation accelerates the remaining hard-to-predict branch chains and most long-latency load chains, maintaining high coverage while reducing backend resource contention. CDE uses a dynamic algorithm that decides how these chains are accelerated. This provides a 9.0% performance improvement without requiring a dedicated execution engine or separate core.

#### 1.4 Contributions

The contributions of this dissertation are as follows:

- A runtime mechanism for tracing long and extremely accurate dependence chains for any branch or load.

- The CDE precomputation thread, that can issue early misprediction flushes for branches whose precomputation result arrives after the corresponding main thread branch is fetched (but before it is executed).

- A mechanism that preferentially fetches and allocates resources for long-latency load chains to improve MLP. Unlike precomputation, these chains commit their results, utilizing backend resources as effectively as possible.

- A unified model for accelerating hard-to-predict branch and long-latency load chains simultaneously. This involves assigning specific branch and load chains to the CDE precomputation thread, ensuring it remains lightweight and timely,

while preferential allocation accelerates the rest of the hard-to-predict branch and long-latency load chains, providing high coverage.

An algorithm that partitions on-core resources for the CDE precomputation thread, the critical stream, and other non-critical instructions. This provides performance comparable to using a dedicated execution engine or separate core with lower energy and power overhead.

#### 1.5 Thesis Statement

Criticality Driven Execution efficiently utilizes existing window resources to preferentially fetch, allocate, and execute critical instructions - issuing early misprediction flushes for hard-to-predict branches and improving Memory Level Parallelism for long-latency loads - thereby reducing the performance penalty associated with most branch mispredictions and cache misses.

#### 1.6 Dissertation Organization

This dissertation contains seven chapters. Chapter 2 provides background on prediction and outlines relevant prior work. Chapter 3 covers the chain construction mechanism, explaining how hard-to-predict branches, long-latency loads, and their chain instructions are identified and stored. Chapter 4 talks about the CDE precomputation thread, explains its benefits, and provides a hardware implementation to support its execution. Chapter 5 introduces preferential allocation, detailing its key features and the micro-architecture support needed. Chapter 6 analyzes chain properties and provides a unified execution model for accelerating hard-to-branch and long-latency loads simultaneously. Chapter 7 concludes the dissertation.

# Chapter 2: Background and Prior Work

#### 2.1 Prediction Mechanisms

#### 2.1.1 Branch Prediction

The branch mispredictions discussed in Section 1.1 are partly caused by branches with complex control flow patterns that are difficult to learn for commercially implemented prediction algorithms such as TAGE [51] and Perceptron [26], even with larger predictor tables. For instance, an infinite-sized TAGE-SCL [52] only provides ~10% reduction [64] in branch mispredictions over a 64KB TAGE-SCL. State-of-theart academic branch predictors such as BranchNet [64] and Whisper [28] attempt to predict these control flows by incorporating offline training techniques using sophisticated learning models. However, they only achieve an additional ~10% misprediction coverage. The remaining branch mispredictions come from data-dependent branches whose targets and directions only correlate with input data, making them inherently challenging to predict with current algorithms.

#### 2.1.2 Data Prefetching

Data prefetchers face similar problems associated with complex load address patterns and data-dependent load addresses. Even large neural data prefetchers [16, 55] only reach ~30% D-cache miss coverage with ~80% accuracy. Commercial products today use stream-prefetchers to deal with LLC misses [20, 25, 57] and use PC-based stride prefetchers [15] at the D-cache. State-of-the-art academic prefetching algorithms [41, 42, 44] only provide ~5% more LLC miss coverage compared to a stream prefetcher (used in the baseline) and struggle to achieve higher coverage without increasing memory traffic significantly.

#### 2.2 Precomputation

Precomputation uses dependence chains to compute branch directions and load addresses ahead of time. If this computation is faster than the main program, the precomputed branch directions override the conditional branch predictor and the precomputed load addresses issue prefetches to the memory subsystem.

#### 2.2.1 Compiler Generated Threads

Early precomputation approaches relied on static analysis to identify frequently mispredicting branches, long latency loads, and their dependence chains, constructing helper threads that operated in a separate context while sharing oncore resources with the main thread. However, these threads often included many unnecessary instructions because runtime control flow tends to follow a limited set of paths, whereas their compile-time analysis accounted for all possible paths to ensure correctness. This led to bloated helper threads that executed too slowly to offer meaningful performance gains. Subsequent work used profiling to remove instructions corresponding to infrequently seen control and data flows, decreasing the helper thread size [9, 27, 31, 63, 65, 66]. However, profiling is not always representative and cannot capture phase behavior, which limits precomputation accuracy.

Lookahead execution [19, 30] similarly uses a "skeleton" or reduced version of the main program (created at compile time) to precompute branch directions and load addresses. It partitions on-core resources to make space for the lookahead thread, but has poor timeliness, similar to helper threads.

#### 2.2.2 Runtime Precomputation Threads

Runtime-only approaches identify hard-to-predict branches, long-latency loads, and their dependence chain instructions dynamically. This reduces the number of instructions in the precomputation thread, improving its timeliness.

Iterative Backward Dataflow Analysis (IBDA) [8] identifies instructions in

long-latency load chains by tagging Register Alias Table (RAT) entries with the PC of the last instruction that writes to each register. However, IBDA cannot track memory dependencies, which are required for tracing chains across calls and returns. Moreover, it only captures a single level of the dependence chain every time the long-latency load is seen, limiting the overall length of the chain. Since IBDA filters the normal fetch stream using the identified PCs, it cannot fetch dependence chain instructions faster than the main thread.

Gupta et al. [21] use a similar technique for identifying hard-to-predict branch dependence chains that contain a single load, followed by a few arithmetic operations, ending at a branch. Tracing these short and simple chains produces timely results, but provides low misprediction coverage. DP-SSMT [10] uses a dataflow walk to trace the dependence chains for loads and branches. The generated thread uses trigger instructions to initiate computation and drive its control flow.

Branch Runahead [46], the prior state-of-the-art in branch precomputation, identifies lightweight and timely dependence chains in applications with simple control flows. However, it struggles with more complex control flow patterns (has lower coverage) and requires a dedicated execution engine to support the parallel computation of these chains. Chapter 4 contains an in-depth comparison against Branch Runahead.

#### 2.2.3 Slipstream

Slipstream [61] and Dual-Core Execution [24] take the concept of precomputation to its limit by running a copy of the program on a separate OoO core. This "ahead thread" executes as fast as possible since it runs unhindered on the separate core without slowing the main thread.

In the most recent Slipstream proposal [59], the ahead thread is constructed at runtime by removing all control-dependent instructions for hard-to-predict branches, allowing it to leverage misprediction-level parallelism [35]. While Slipstream offers

improved coverage for both loads and branches, the ahead thread is heavy-weight (executing over 75% of the program's dynamic instructions) and requires a dedicated OoO core to maintain high throughput for the ahead thread. Using a separate core reduces performance as the delay associated with communicating precomputed branch directions and load addresses to the core running the main thread hurts timeliness. The additional core doubles the area and power overhead, and the extra instructions increase energy consumption. Chapter 6 evaluates the performance and energy of a Slipstream-like approach with the CDE dependence chains.

#### 2.2.4 Using Precomputation to Resolve Branches Early

Prior work uses precomputation to override the branch predictor, providing no benefit if the corresponding main thread branch has already been fetched. This is because they use a unified queue or multiple per-branch queues to forward precomputed directions to the branch predictor. These queues are expensive as they buffer hundreds of predictions per branch and have multiple write ports, as several branches in the precomputation thread can finish executing together.

Implementing early resolution with these queues (in addition to overriding the branch predictor) requires support for simultaneous reads from multiple frontend pipeline stages. Alternatively, the in-flight branch queue and precomputed branch queues can be scanned in parallel to match precomputation thread branches to their main thread counterpart. This enables early resolution for branches that have entered the backend as well. However, both solutions increase the hardware cost and complexity of these queues as they require fully-associative lookups over large queue sizes (over 300 entries long). Farcy et. al. [17] use the scanning approach but do not discuss its implementation overhead. Gupta et.al. [21] only provide a few fixed flush points in the frontend. The cost of these queues also prevents prior work from precomputing branch targets for indirect branches.

CDE does not have this limitation as it uses synchronized timestamps: the

sequence number for a branch in CDE's precomputation thread is the same as the sequence number assigned to the corresponding main thread branch. This allows CDE to issue early misprediction flushes by reusing existing flush mechanisms. The details are covered in Chapter 4.

#### 2.3 Runahead Execution

Loads that access memory generally take several hundred cycles to execute. Most load addresses cannot be precomputed early enough to hide the full memory latency. Runahead execution instead initiates memory accesses for future independent loads in parallel during full window stalls. This improves memory bandwidth utilization (if the load addresses are correct), providing most of the benefit associated with prefetching the load. However, traditional variants of Runahead are only active during full window stalls, limiting their effectiveness in workloads with fewer stall cycles. This effect has become more prominent over the years as the window size continues to grow.

The original Runahead work [37] executes all instructions in Runahead mode and cannot discover much MLP in processors with a large ROB. Later work [22, 38, 39] only executes load chains in Runahead mode and uncovers more MLP. However, these chains have low coverage, often produce inaccurate memory addresses, and are still limited by shorter full window stalls in many benchmarks.

"Decoupled" versions of Runahead [23, 40] execute load chains on a dedicated execution engine and are not limited to full window stalls. These are similar to precomputation-based techniques and have the same pitfalls: they use short chains with specific dataflow properties that work well for applications with simple control flows but struggle on more irregular applications. Chapter 5 contains a quantitative comparison against Runahead execution.

#### 2.4 Compiler Solutions

Compilers can identify hard-to-predict branches and long-latency through profiling. They can rearrange code by unrolling loops and hoisting hard-to-predict branches or long-latency loads to compute them earlier in the program or to improve parallelism. This eliminates the hardware overhead of constructing and storing dependence chains at runtime. However, purely compiler-based solutions have a few major flaws. They rely on profiling, which is not always representative. Hoisting distance is limited by architectural register pressure [62] as the associated dependence chain instructions also need to be moved. Further, the optimal instruction ordering depends on detailed microarchitectural parameters that may not be available at compile time.

CRISP[33] is a lightweight compiler solution with minimal hardware support that profiles workloads in a data center environment and prioritizes hard-to-predict branch and long-latency load dependence chains in the scheduling logic. However, its benefit is limited as it only speeds up their execution by a few cycles.

Control-Flow Decoupling [53] uses the compiler to hoist the control-flow computation within a loop. The hoisted code inserts computed branch directions ahead of time into a hardware queue read by the rest of the instructions. This is challenging to do in the absence of loops or for loops with fewer iterations, as significant code duplication is required to account for all control flows leading to a branch.

#### 2.5 Other Related Work

Speculative multi-threading [34] splits the program into speculative threads at compile time and executes these threads on a different core to improve Instruction-Level Parallelism (ILP). It leverages the compiler to find good points to parallelize code. These threads are not always useful since instruction criticality cannot be accurately computed at compile time. Balasubramonian et al. [5] use a similar "future

thread" that executes (but does not commit) on a partitioned section of the core and forwards register values to the main thread.

Long Term Parking [50] and Shelf OoO Execution [56] leverage instruction criticality to improve the efficiency of Reservation Stations, but cannot extract parallelism beyond the capacity of the ROB. Agarwal et al. [3] use instruction criticality and control independence to reduce in-order fetch bottlenecks. Continual Flow Pipelines [58] finds independent long-latency load chains in a short loop and uses a ROB-less architecture [4] to enable a larger instruction window for long-latency loads.

#### 2.6 Baseline Out-Of-Order Core

| Core       | 3.2GHz, 8-wide issue, 12 cycle FE latency, Support for MOV elimination    |

|------------|---------------------------------------------------------------------------|

|            | 512 Entry ROB, 256 Entry Reservation Station, 16-wide retire              |

|            | 16 Execution Ports (6-ALU, 2-ST, 4-LD, 4-FP/VEC), Oldest-first scheduling |

|            | (3-ALU with BR, 3-ALU with SHFT&MUL, 2-FP with MUL, 2-FP with DIV)        |

|            | 400 Physical Regs, 192 entry load queue, 128 entry store queue            |

| Predictors | 64KB TAGE-SC-L[51], 32-entry Fetch Queue                                  |

|            | History-based indirect branch predictor, RAS                              |

|            | 1 taken per cycle, 8K entry BTB                                           |

| Caches     | 32KB 8-way L1 I-cache (4-cycle access) 1R, 1W port (2 banks)              |

|            | 48KB 12-way L1 D-cache (4-cycle access), 64B lines (4R 2W ports)          |

|            | 512KB 16-way L2 cache (12-cycle access)                                   |

|            | 1MB 16-way LLC (18-cycle access), 32 MSHRs                                |

| Prefetcher | Stream Prefetcher, 64 Streams (always on),                                |

|            | Feedback Directed Prefetching to throttle prefetcher                      |

| Memory     | DDR4_2400R: 1 rank, 2 channels                                            |

|            | 4 bank groups and 4 banks per channel                                     |

|            | tRP-tCL-tRCD: 16-16-16                                                    |

|            |                                                                           |

Table 2.1: Core parameters

The baseline OoO core evaluated in this dissertation uses the x86 ISA. It has an 8-wide frontend with a decoupled branch predictor [47] that can predict up to one taken branch or sequential instructions spanning 128B per cycle. Fetch addresses generated by the decoupled branch predictor are filled into a Fetch Queue. The Fetch unit uses Fetch Queue addresses to read up to two sequential cache lines from the Instruction Cache (I-Cache). The Decode, Rename, and Allocation stages handle up to

8 micro-operations (uops) per cycle, with 128-entry instruction buffers between Fetch and Decode. The frontend is 12 stages deep, and the minimum fetch-to-resolution latency for a branch is 15 cycles. The load-to-use latency for D-Cache (Data-Cache) hits is 5 cycles. The processor contains a unified Reservation Station with oldest-first scheduling. All the parameters are listed in Table 2.1.

## Chapter 3: Critical Chain Construction

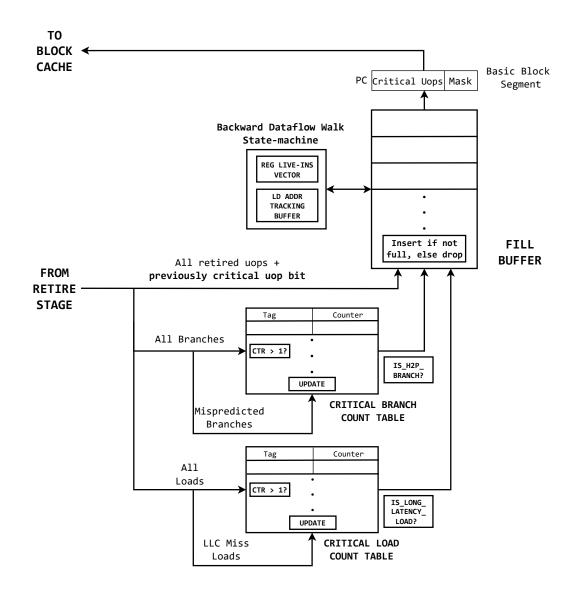

CDE identifies critical instructions at runtime in two steps. First, it detects hard-to-predict branches and long-latency loads via a counter-based mechanism. Then it uses these loads and branches as initiation points for a Backward Dataflow Walk to trace their dependence chains. The identified critical instructions are broken into basic block segments and stored in a Block Cache. The CDE precomputation thread and preferential allocation eventually use these entries to reconstruct the constituent hard-to-predict branch and long-latency load chains as needed. This mechanism was first proposed and later used in my published work[13, 14].

## 3.1 Marking Hard-To-Predict Branches and Long-Latency Loads

A small subset of static branches and loads (256) account for over 95% of branch mispredictions and LLC misses<sup>1</sup>. Prior work uses counter-based techniques [11, 12, 46] to track these hard-to-predict branches and long-latency loads. These counters capture branches and loads above a fixed accuracy threshold. I adapt these techniques to build two "Critical Count Tables" that mark all branches and loads above a specified MPKI (mispredictions/misses per kilo instructions) threshold instead.

#### 3.1.1 Critical Count Tables

The Critical Count Tables are independent structures updated at retirement. The Critical-Branch Count Table tracks direction and target mispredictions for direct and indirect branches. It is an 8-way set-associative table containing 256 entries, indexed with the branch Program Counter (PC). Each entry in the table has a 3-bit saturating counter. An entry is created for a branch when it mispredicts, with its

<sup>&</sup>lt;sup>1</sup>The numbers were averaged across Simpoints of length 200M each

counter value initialized to 1. Each subsequent misprediction at that PC increments the counter. A branch is considered hard-to-predict if it has an entry in the Critical-Branch Count Table and its counter value exceeds 1.

All counters in the table are decremented periodically. This ages out counters for branches below a specified MPKI threshold. For example, with a decrement period of 5000 (i.e., the counter value is decremented every 5000 instructions), counters for branches with MPKI below 0.2 will tend towards 0 as it is decremented more often than mispredicts are seen.

The Critical-Load Count Table works similarly. When a load misses in the LLC, an entry is created. The corresponding counter is incremented on subsequent LLC misses caused by the same load PC, and all counter values are periodically decremented.

Thresholding based on MPKI instead of accuracy (which prior work uses) more directly captures which branches and loads contribute to slowdowns within an instruction window. However, this effect is only prominent in workloads with larger footprints and does not have a noticeable impact on the SPEC CPU2017 and GAP benchmarks.

The table parameters determine the number of chains accelerated. This affects the coverage and timeliness of the execution models, and is evaluated in Section 4.6 and Section 5.5.

## 3.2 Identifying Dependence Chain Instructions

Dependence chains for marked hard-to-predict branches and long-latency loads are traced using a modified version of the Backward Dataflow Walk [10, 22]. For this, instructions are first collected in a post-retire buffer called the Fill Buffer.

#### 3.2.1 Fill Buffer

The Fill Buffer holds up to 512 micro-ops (uops). Uops are added to the buffer after retirement and stored in program order. Retired branches and loads query the Critical Count Tables before being added to the Fill Buffer. An entry in the Fill Buffer contains the decoded uop, memory addresses accessed by the uop, whether it was marked a hard-to-predict branch or long-latency load (as set by the Critical Count tables), and a bit signifying that the uop is in the marked dependence chains (initially set to 0). This is summarized in Table 3.1. Note that the Fill Buffer operates at the level of uops to avoid decoding chain instructions when they are eventually used. For simplicity, all the examples in this dissertation contain instructions with a single uop.

| PC      | Decoded Uop | Load/Store Address | H2P BR | Long-Lat LD | Chain bit |

|---------|-------------|--------------------|--------|-------------|-----------|

| 32 bits | 64 bits     | 32 bits            | 1 bit  | 1 bit       | 1 bit     |

Table 3.1: Fill Buffer entry

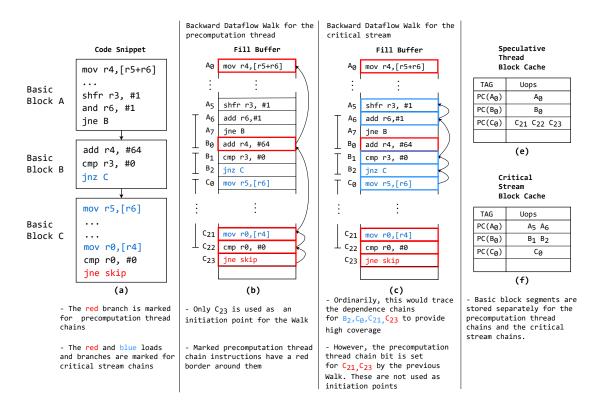

#### 3.2.2 Backward Dataflow Walk

The Backward Dataflow Walk identifies the minimal set of instructions needed to compute the marked hard-to-predict branches and long-latency loads. It is initiated when the Fill Buffer is full. The rest of this section explains the chain identification process in the context of hard-to-predict (H2P) branches, but functions similarly for long-latency loads.

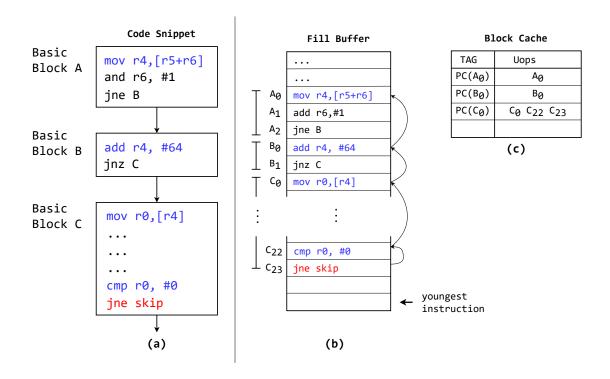

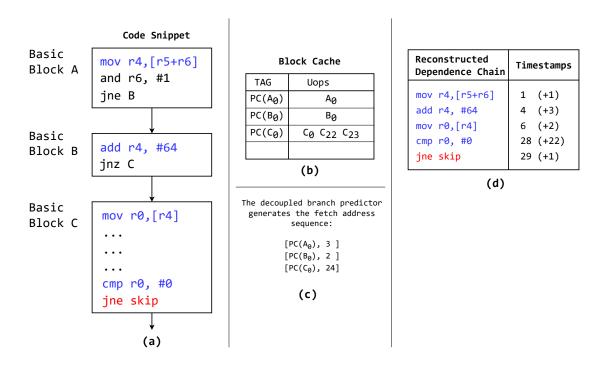

The example in Figure 3.1.a shows a code segment containing an H2P branch, with its assembly and control flow diagram. Figure 3.1.b shows how the Fill Buffer is populated when this code segment is executed and retired. The H2P branch is marked in red. When the Fill Buffer is full, the Backward Dataflow Walk begins. Starting at the youngest instruction, the Fill Buffer is traversed one entry at a time until an H2P branch is encountered. Registers and memory addresses needed to

Figure 3.1: Identifying dependence chain instructions in the Fill Buffer

compute that branch are then added to a "Source List". In the example,  $C_{23}$  is the first H2P branch encountered during the Backward Dataflow Walk, and the condition code register (RFLAGS for x86) is added to the Source List.

Any instruction that writes to a register or memory location in the Source List is part of the H2P branch dependence chains. Thus,  $C_{22}$  is marked as a dependence chain instruction (blue). At the same time, the  $C_{22}$ 's destination register (RFLAGS) is removed from the Source List, and  $C_{22}$ 's source register (R0) is added instead. This ensures that the Source List tracks the minimum set of live-ins needed to compute the marked H2P branches.

Continuing upwards,  $C_0$  is marked as a dependence chain instruction, and the Source List is modified to contain register R4 and memory location [R4]. The Backward Dataflow Walk continues until it reaches the oldest instruction in the Fill Buffer, marking all the instructions highlighted in blue. **Note that chains for all**

branches marked as H2P, including multiple dynamic instances of the same H2P branch, are traced simultaneously via this mechanism. In contrast, prior work [10, 22, 46] only used the Backward Dataflow Walk to trace dependence chains one branch at a time and terminated the Walk after seeing a second instance of the branch being traced, limiting their chains to short loops.

#### 3.2.2.1 Hardware Implementation

Uops are initially added to the Fill Buffer after the Decode stage since the decoded uops are not available at Retire (these are overwritten on a misprediction flush). After retiring, uops populate the rest of the fields in their Fill Buffer entries. Memory addresses are read out when the corresponding Load or Store Queue entry is retired. Alternatively, after address generation for a uop is completed, the addresses with their corresponding sequence numbers can be saved in a separate buffer until retire (indexed by sequence number and does not require associative lookups).

The Backward Dataflow Walk takes  $\sim 500$  cycles and is managed by a state machine. Register dependencies are tracked using a bit-vector with one bit perarchitectural register. Memory dependencies are tracked using a small 32-entry buffer that records load addresses. Together, these structures form the "Source List" mentioned earlier.

Instructions retired during the backward Dataflow Walk are discarded. The Fill Buffer thus only samples a portion of the retired instruction stream. Performance is not sensitive to the duration of the Backward Dataflow Walk, and the associated structures do not need multiple access ports to perform the walk faster or capture all retired instructions. The Fill Buffer size does not affect performance significantly (<0.5% change) as I use bit-masks to extend dependence chains, as explained in Section 3.5.

## 3.2.3 Storing Dependence Chain Instructions

The marked dependence chain instructions (including hard-to-predict branches, whose chain bit is also set) are split into basic block-sized segments and stored in a "Block Cache". Block Cache entries are tagged with the PC of the first instruction in that basic block (Figure 3.1.c). These entries are later stitched together using predictions generated by the branch predictor to reconstruct the dependence chains at fetch time. This is discussed in Section 3.7.

## 3.3 Tracking Memory Dependencies

The Source List tracks memory dependencies as correlated loads and stores affect chain accuracy. This is most commonly seen when an H2P branch is within a function body. In such cases, the function's input variables are often part of the dependence chain. The push and pop operations that communicate these variables need to be included in the dependence chain to trace instructions beyond the function boundary.

Unlike register dependencies, memory addresses corresponding to correlated load-store pairs can change over time. Thus, incorporating memory dependencies sometimes increases chain size without improving its accuracy. However, the overall improvement in the length and accuracy of the dependence chains makes up for this in most benchmarks.

# 3.4 Tracing Longer Dependence Chains

Longer dependence chains improve timeliness as they initiate the computation for the corresponding hard-to-predict branches and long latency loads earlier. However, the maximum chain length that can be traced is limited by the Fill Buffer size and the position of the H2P branch in the Fill Buffer. Using chain instructions as initiation points for the Backward Dataflow Walk (the next time they are seen in the

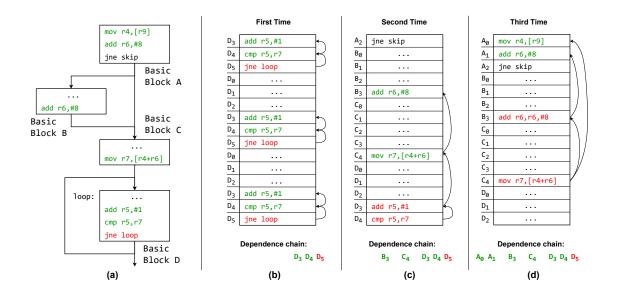

Figure 3.2: Tracing longer dependence chains using previously marked instructions

Fill Buffer) overcomes this limitation.

The example in Figure 3.2.a depicts this. This code snippet contains a loop branch that is H2P. Only a few instructions in the dependence chain of this H2P branch can be traced the first time it is seen in the Fill Buffer (Figure 3.2.b). The main thread keeps track of this information, and corresponding uops preemptively set their chain bit the next time they enter the Fill Buffer. Figure 3.2.c depicts a future Fill Buffer iteration. The Backward Dataflow Walk in this case is initiated at dependence chain instructions (highlighted in red this time) instead of an H2P branch. Additional instances of the Backward Dataflow Walk (Figure 3.2.d) trace more and more of the dependence chain. The individual basic block segments are then stitched together, which allows CDE chains to span thousands of instructions.

# 3.5 Combining Chains across Multiple Control Flows

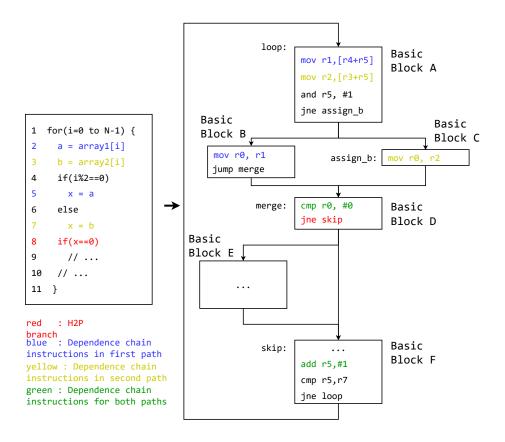

An H2P branch can have different dependence chains for each control flow leading up to it. Figure 3.3 shows such an example. Under the control flow A-B-D,

Figure 3.3: Tracing dependence chains across multiple control flows

the first instruction in basic block A is part of the dependence chain (in blue) for the H2P branch (in red). For A-C-D, the second instruction in basic block A is part of the dependence chain (in yellow). Saving the longest or the most recent dependence chain produces incorrect results if the saved chain does not match the actual control flow during fetch. Saving all possible chain versions is not viable as each additional branch added to the control flow (branch at the end of block A, for example) exponentially increases the number of possible chains.

Combining chains from multiple paths ensures the chain is correct across all these paths. This is done by storing a bit mask for each basic block that specifies which instructions in that basic block are part of H2P branch chains. Different versions of this bit-mask can be combined by bit-wise ORing them. In Figure 3.3, two masks are

generated for basic block A: 1000 for control flow A-B-D and 0100 for control flow A-C-D. The "1" in the bit mask indicates that the instruction is part of the chain. After bit-wise ORing, both the first and second instructions in basic block A are marked and saved in the Block Cache. This adds extra instructions (not needed to compute the H2P branch) to both paths but ensures the H2P branch chain is correct under both control flows. The masks are stored as part of the Block Cache entry for that basic block.

## 3.6 Steady State Operation

Figure 3.4 shows an overview of all the components. The Critical Count Tables are always active; retired branches and loads that access memory continuously update these tables independently of the Fill Buffer. Two additional bits in the ROB are added to track mispredicted branches and loads that miss in the LLC, which filter out the branches and loads that update the Critical Count Tables. In parallel, the Fill Buffer captures retired instructions (while querying the Critical Count Tables) until it fills up. When full, the Backward Dataflow Walk is initiated, and the identified chains uops are filled into the Block Cache.

Main thread instructions that were part of the CDE precomputation thread or the critical stream are marked with an additional bit in the ROB. This bit is carried along to the Fill Buffer and preemptively sets the chain bit in the Fill Buffer. This allows the Backward Dataflow walk to be initiated at previously marked chain uops, tracing longer chains as discussed in Section 3.4.

#### 3.6.1 Block Cache

Uops with their chain-bit set after the Backward Dataflow Walk are divided into basic block segments and stored in the Block Cache. The Block Cache has 512 entries and is divided into a tag store and a data store. The tag store holds a 40-bit tag (PC of the first instruction in the basic block). The data store contains decoded

Figure 3.4: Implementation overview: Tracing dependence chains

dependence chain uops (4B per uop on average), the bit-mask (32 bits long), and the number of non-chain uops skipped (which are used for computing timestamps at Fetch).

On a tag match, the existing, older basic block segment is read out. Its bitmask is ORed with the bit-mask for the incoming, newer basic block segment. The corresponding uops are combined, and this combined basic block segment and bitmask are then written to the Block Cache. Note that the fill operation is off the critical path and does not impact cycle time. This combines chains across multiple control flows as discussed in Section 3.5.

In most benchmarks, over half the basic block segments contain no chain uops for hard-to-predict branch and long-latency load chains. To optimize storage capacity, a smaller 256-entry tag store is reserved exclusively for basic block segments with no dependence chain uops. These do not need data store entries as they contain no chain uops and their bit-masks are zero. This tag store captures cases where a dependence chain traverses intermediate basic blocks with no chain uops and directs the Fetch unit not to terminate the dependence chain, as there may be more chain uops past the empty basic block segments.

Periodically resetting the bit-masks: Some control flow patterns are only observed during specific execution phases. Dependence chains captured with older control flows may not be valid after a phase change and therefore need to be removed to keep the chains lightweight. This is done by periodically resetting the bit-masks in the Block Cache and overwriting the existing basic block segments. The periodic reset ensures that future Backward Dataflow Walks do not use the bit-mask instructions as initiation points if they are no longer critical in the current execution phase. A reset period of 500K instructions worked best for performance.

## 3.7 Reconstructing the Dependence Chains at Fetch

Fetch addresses generated by the decoupled branch predictor in the baseline OoO core are forwarded to the Block Cache, which has a dedicated Fetch unit coupled to it. The Block Cache retrieves the corresponding basic block segments at these addresses and stitches them together to reconstruct the stored dependence chains.

Figure 3.5 shows how this works for the example in Figure 3.1. The control flow diagram for the code and corresponding Block Cache entries are repeated in

Figure 3.5: Fetching uops from the Block Cache

Figure 3.5.a and Figure 3.5.b. After the Backward Dataflow Walk completes, the program control flow reaches the same code snippet again, as it is part of a loop or a function that is called repeatedly<sup>2</sup>.

The baseline decoupled branch predictor uses the current program counter (PC) to generate the next address at which instructions are fetched and the number of instructions to be fetched at that location. For this code snippet, the fetch addresses generated are shown in Figure 3.5.c. This takes 3 cycles, as the branch predictor has a throughput of one taken branch per cycle.

These fetch addresses are sent to the I-Cache (for the main thread) and the Block Cache in parallel. On a hit in the Block Cache, the CDE precomputation thread (or the critical stream in case of preferential allocation) is initiated. The chain uops

<sup>&</sup>lt;sup>2</sup>Note that CDE can only improve a hard-to-predict branch or long-latency load if its dependence chain is seen multiple times

corresponding to the fetch address are read out of the Block Cache in 3 successive cycles and stitched together to reconstruct the stored dependence chain as seen in Figure 3.5.d. Regular fetch for this example would require more than 3 cycles as the instructions in basic block C cannot be fetched in a single cycle.

The number of skipped non-chain uops stored in the Block Cache is used to compute the timestamp for the chain uops. The computation is done in parallel with the rest of the Fetch stage processing and does not impact the critical path. This approach of capturing and stitching together basic block segments is similar to prior work on trace caches [18, 45, 48], except we only do this for critical instructions.

# Chapter 4: Speculative Precomputation for Hard-To-Predict Branch Chains

Prior work has shown hard-to-predict branch chains usually have shorter latencies compared to other instructions and run faster when executed independently. To speed up their computation, I combine hard-to-predict branch chains into an independent, speculatively executed thread that precomputes branch directions.

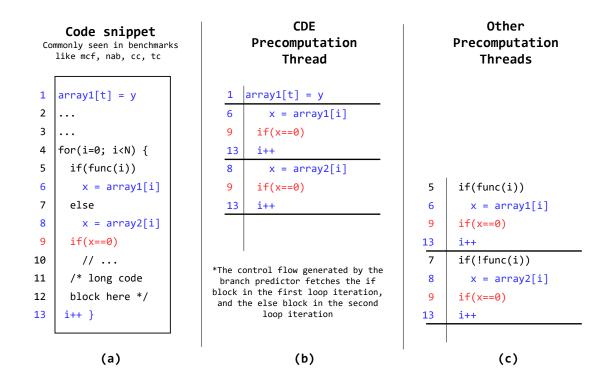

## 4.1 CDE Precomputation Thread

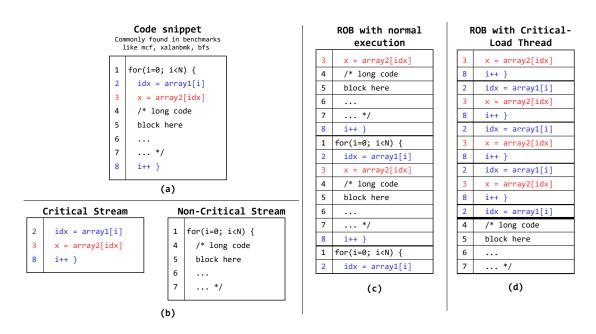

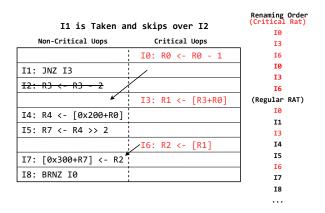

Figure 4.1: CDE precomputation thread example

The example in Figure 4.1 shows how the CDE precomputation thread works. The code snippet in Figure 4.1.a contains a hard-to-predict branch on line 9 (high-lighted red). The control flow generated by the branch predictor fetches and executes

the if code block in the first loop iteration, and the else code block in the second loop iteration.

The CDE precomputation thread, shown in Figure 4.1.b, is constructed by stitching together basic block segments at fetch addresses generated by the branch predictor as explained in Section 3.7. It contains fewer instructions compared to the main thread and can thus be fetched faster (limited only by the branch predictor throughput). Given enough resources, the CDE precomputation thread executes multiple instances of the hard-to-predict branch and issues the corresponding misprediction flushes (if any) a few cycles before the main thread. The earlier the precomputation thread starts, the more opportunities it gets to run ahead of the main thread, saving more cycles of misprediction penalty.

When a precomputation thread branch is found to be mispredicted, the existing infrastructure uses the branch timestamp (generated during chain reconstruction) to issue a pipeline flush. This flushes instructions younger than the mispredicted branch in both threads. Fetch for both threads then resumes at the same point, i.e., their states are synchronized. The precomputation thread starts running ahead again, looking for the next misprediction. Thus, the CDE precomputation thread reduces the time between successive mispredictions.

#### 4.1.1 Benefits of using the Main Branch Predictor

Non-H2P intermediate branch direction can affect which instructions are part of hard-to-predict branch chains. The branch on line 5 in Figure 4.1 is one such example. Prior work attempts to deal with these branches by either assuming the majority direction (which decreases chain accuracy) or by also precomputing their dependence chains (which adds many additional instructions, decreasing timeliness). Most recent work, including the prior state-of-the-art, Branch Runahead, chose the later approach (Figure 4.1.c).

The CDE precomputation thread, on the other hand, does not need to compute

intermediate branch directions. It uses fetch addresses generated by the main branch predictor (TAGE-SCL) to stitch together basic block segments that comprise the traced dependence chains. TAGE-SCL predicts non-H2P intermediate branches with very high accuracy (>99.9%) and the chains reconstructed using these predictions are thus also accurate. TAGE-SCL also predicts many hard-to-predict branches with over 80% accuracy, allowing the precomputation thread to correctly fetch instructions past them without waiting for the H2P branch to resolve.